Heterogenous

System-In-Package (HSiP)

Quality - Certifications

Quality Policy

To meet our customers’ expectations and applicable regulatory / statutory requirements through delivery of products that reflect continuously improved quality, service, and reliability and maintains the effectiveness of the Quality Management System.

- DMEA Accredited Trusted Foundry

- ITAR Certified

- ISO-9000:2015 Certified

- Small Business Enterprise

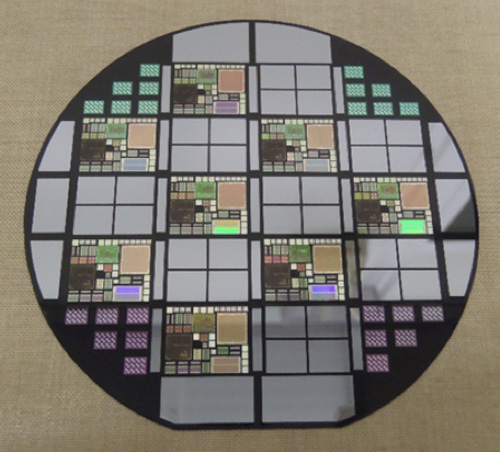

HSiP as a FO-WLP Technology

- HSiP is capable of simple, single-die, Redistribution Layer (RDL) fabrication

For additional technical information please inquiry at info@i3technologygroup.com

HSIP Reliability Baseline Conclusions**

HSIP technology offers tremendous flexibility to accommodate different die types, sizes to produce a high performance high density multi-chip package using FOWLP.

Process capable to produce a flat HSIP with good electrical circuit when using RTV-03 conditions (low bake, longer times).

** As presented by i3 Microsystems, Inc. at IMAPS 2020

Heterogeneous IC Integration

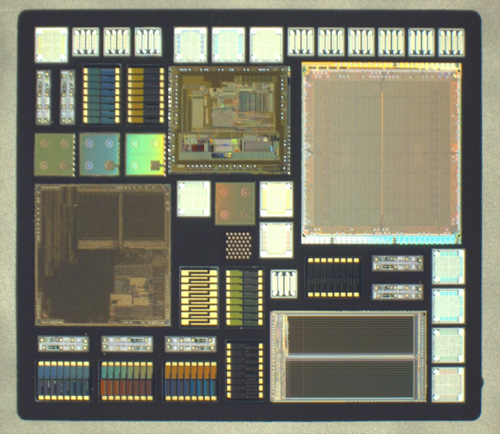

As system performance requirements and complexity continue to grow with an emphasis on SWAP, it is inevitable that heterogeneous IC integration will become the industry standard. The conventional monolithic system on a chip is just not economically feasible to integrate all of the functionality onto one universal technology node. FPGA alone cannot include mixed signal, analog and RF functions as these technologies have vastly diverging requirements. Attempts have been made to combine programmable logic with analog and memory. There is either too little memory, logic or analog performance. These result in a very restricted product offering and as such limit the range of applications that will fit within these constraints. A much more versatile product results from the integration of components that have been constructed on an optimum technology node for each function. The integration of sensors (MEMs), RF, A/D, CPU, ASIC, DRAM, Flash and III-V materials into a single module produces a SIP with far higher functionality, better SWAP, and performance unachievable with any other approach.

Without surface mounts

With surface mounts

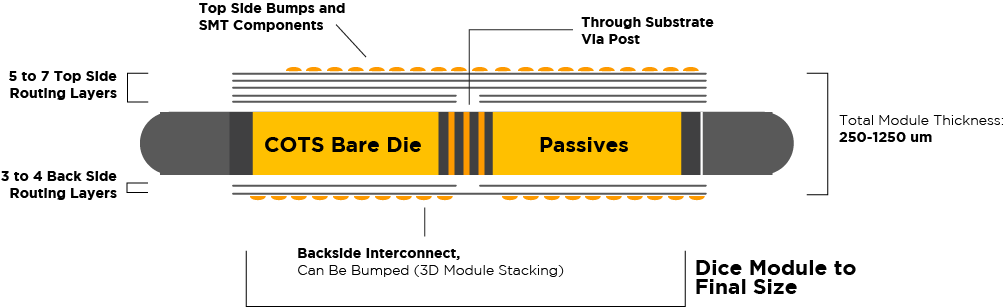

SWaP and Benefits

- Driving the largest reductions in Size, Weight and Power (SWaP)

- Stacks as a subsystem – up to three slices

- Scalable to larger wafer formats for future volume production demands

- Embedded Die Interposer Technology

- Can incorporate extracted/recovered die for faster prototyping and lower volume orders

- Potential to connect all device technologies – MEMs, sensors, memory, analog, controllers etc.; and all source substrates: Si, GaAs, InP, glass devices – into one package

- Uses TMV (Thru Mold Via) with no wire bonds or separate interposers

- Up to 7 interconnect metal layers per side

- Able to be brought out to BGA or SMT interfaces on both sides

- Developed by Draper Laboratory for DoD applications, and HSiP is now available under license to i3 for wider DoD, commercial, or industrial uses

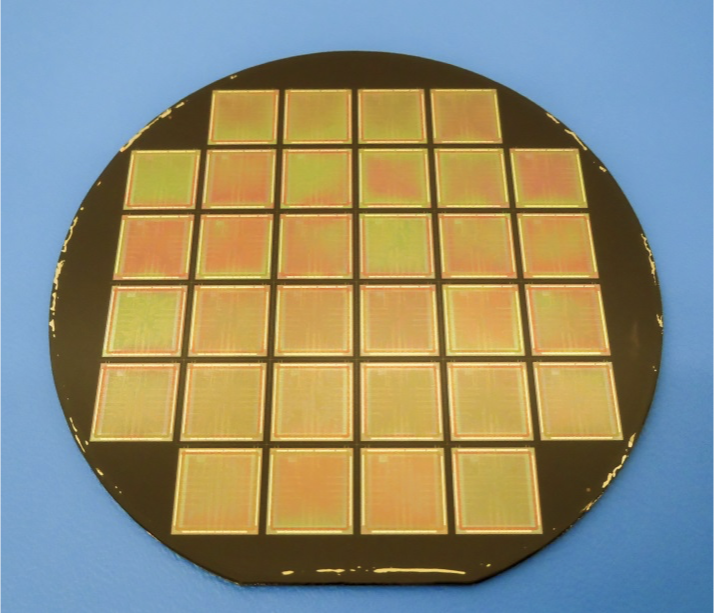

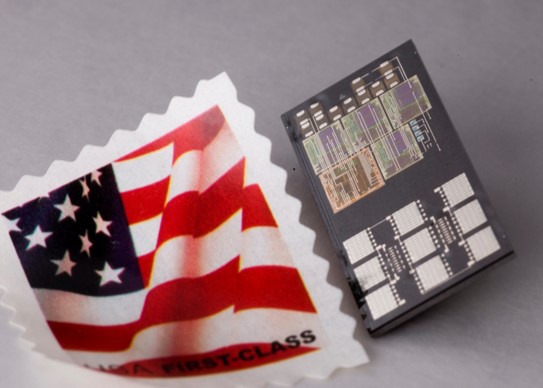

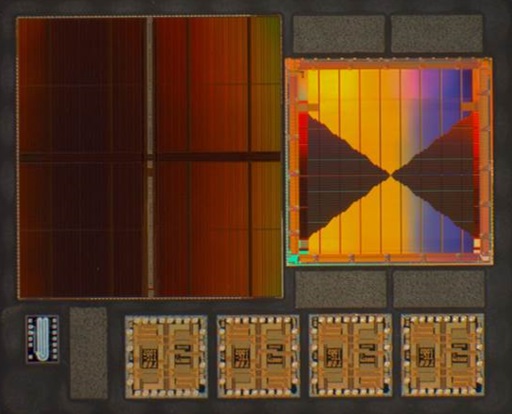

HSiP Examples

Heterogeneous Multichip Modules are a chips-first, fan out, wafer level package.

- Heterogeneous IC integration

- Embedded active and passive die in the smallest volume form factor

- Ultra-high density interconnect

- Front-to-back interconnect TSVs (Through Substrate Vias)

- More robust system design than commercial off-the-shelf

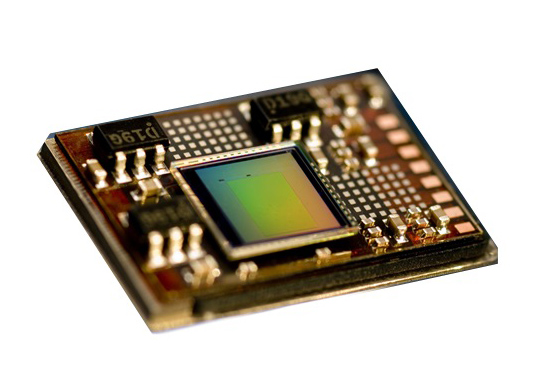

Single Sub-Module Overview

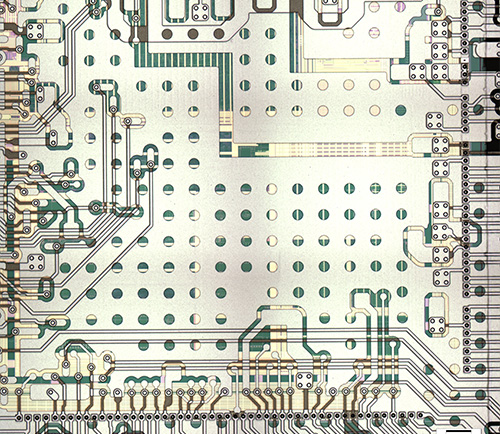

Interconnect Fabric

Seven interconnect layers are possible on both the frontside and the backside, allowing for design possibilities such as controlled impedance transmission lines, power/ground bus, and signal line shielding for crosstalk isolation.

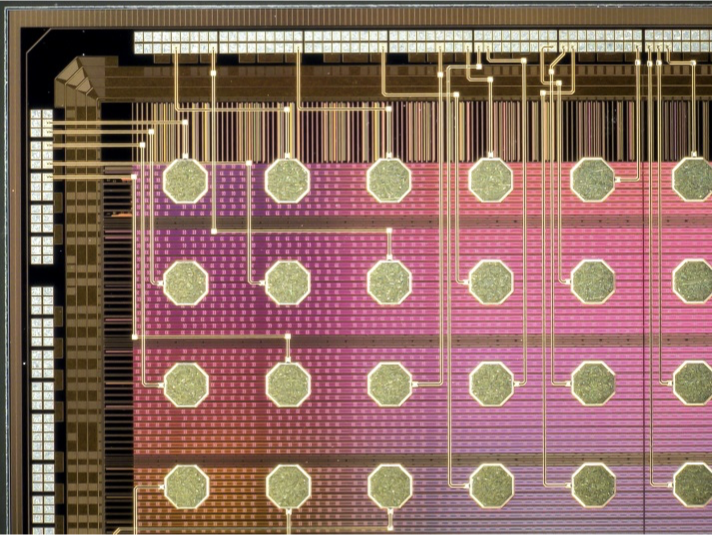

Multichip module, bare die, pre-interconnect

Multichip module, post-interconnect

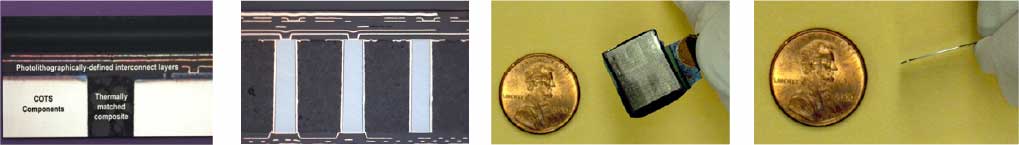

3D Stacking with Heterogeneous MCMs

Individual Multichip Modules can be stacked for higher performance in the same footprint.

Single Layer Module

Frontside to Backside Routing: TSV's

Fabricated Backside Interconnect

3D Stack of Single Layer Modules